# Departament d'Electrònica

# ANALYSIS OF INTEGRATED TRANSFORMERS AND ITS APPLICATION TO RFIC DESIGN

Tesi doctoral presentada per a l'obtenció del títol de doctor Enginyer en Electrònica

Josep Cabanillas Costa

Director:

José M. López Villegas

#### Universitat de Barcelona

#### Departament d'Electrònica

# Analysis of Integrated Transformers

### and its Application to RFIC Design

Memòria presentada per optar al títol de Doctor en Enginyeria Electrònica.

Programa de doctorat: Enginyeria i Tecnologia Electrònica

Bienni: 98-00

Barcelona, Octubre del 2002

Autor:

Josep Cabanillas Costa

Director de Tesi:

Dr. José M. López Villegas

En José M. López Villegas, Professor Titular de la Facultat de Física de la Universitat de Barcelona,

#### CERTIFICA:

que la memòria "Analysis of Integrated Transformers and its Application to RFIC Design", que presenta en Josep Cabanillas Costa per optar al grau de Doctor en Enginyeria Electrònica, s'ha realitzat sota la seva direcció.

Dr. José M. López Villegas

Josep Cabanillas Costa

# **Contents**

| Introduction                                          | I-1  |

|-------------------------------------------------------|------|

| 1 Wireless World. Long and short range communications | I-1  |

| 2 The RF integrated design. The RF front-end          | I-3  |

| 3 RF architectures. Direct-conversion                 | I-8  |

| 4 Future trends                                       | I-12 |

| 5 Organization and goals of this thesis               | I-14 |

| 6 References                                          | 1-17 |

| Chapter 1. Integrated Transformers                    | 1-1  |

| Introduction                                          | 1-1  |

| 1.1 Integrated inductors                              | 1-3  |

| 1.1.1 Silicon technologies for RF applications        | 1-4  |

| 1.1.2 Modelling of integrated inductors               | 1-6  |

| 1.1.3 Eddy currents in integrated inductors           | 1-7  |

| 1.2 Integrated transformers                           | 1-10 |

| 1.2.1 Transformer topologies                          | 1-11 |

| 1.2.2 Transformer modelling                           | 1-13 |

| 1.2.3 Eddy currents in integrated transformers        | 1-15 |

| 1.2.3 Capacitive effects                              | 1-21 |

| 1.3 References                                        | 1-25 |

| Ch           | 2-1                                                       |      |

|--------------|-----------------------------------------------------------|------|

| Introduction |                                                           | 2-1  |

| 2.1          | Phase noise theory                                        | 2-5  |

| 2.2          | Circuit analysis of the transformer-based resonator       | 2-8  |

|              | 2.2.1 Electrical Analysis                                 | 2-8  |

|              | 2.2.2 Even-Odd Analysis                                   | 2-12 |

| 2.3          | EM analysis of the transformer-based resonator            | 2-14 |

| 2.4          | Comparison between series and parallel resonators         | 2-18 |

| 2.5          | Transformer optimization                                  | 2-23 |

| 2.6          | Oscillator design and measurement                         | 2-27 |

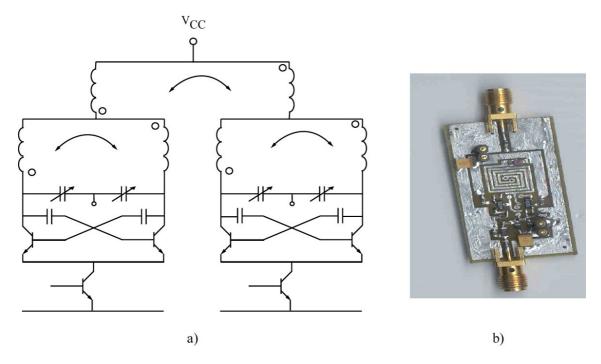

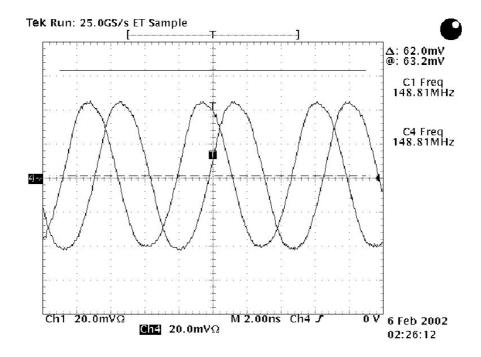

|              | 2.6.1 Designing oscillators based on N-coupled resonators | 2-27 |

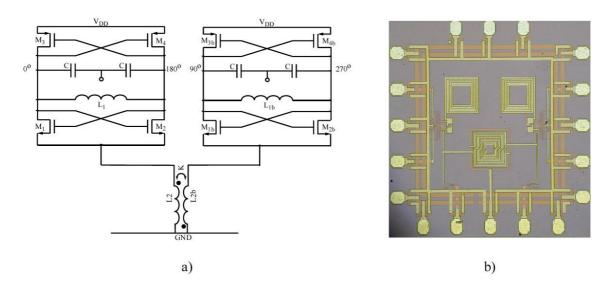

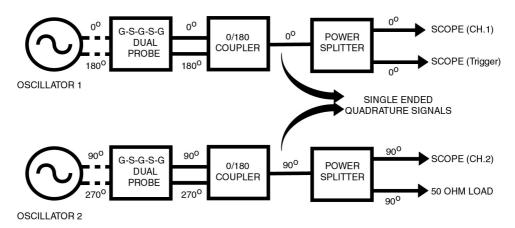

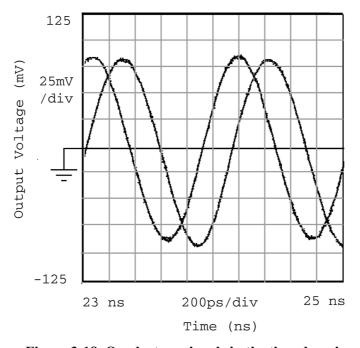

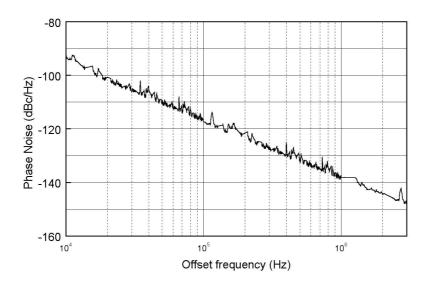

|              | 2.6.2 Prototype design and test                           | 2-29 |

| 2.7          | References                                                | 2-33 |

| Ch           | apter 3. Quadrature Oscillators                           | 3-1  |

| Int          | roduction                                                 | 3-1  |

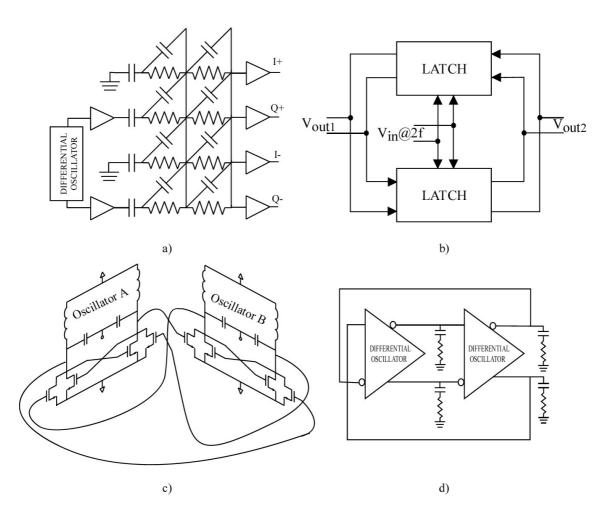

| 3.1          | Quadrature oscillators topologies                         | 3-3  |

| 3.2          | Non-linear analysis of a NMOS cross-pair                  | 3-6  |

| 3.3          | Injected oscillators                                      | 3-16 |

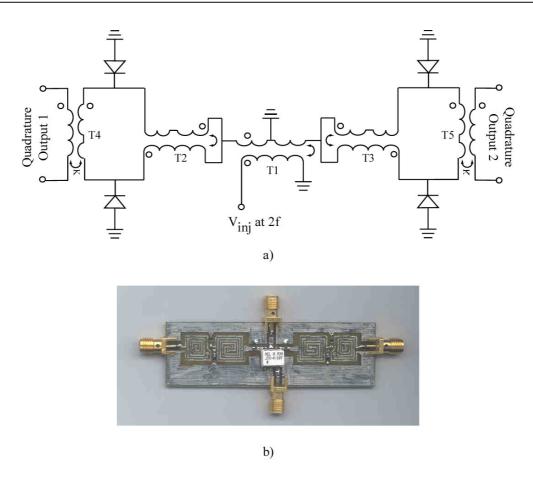

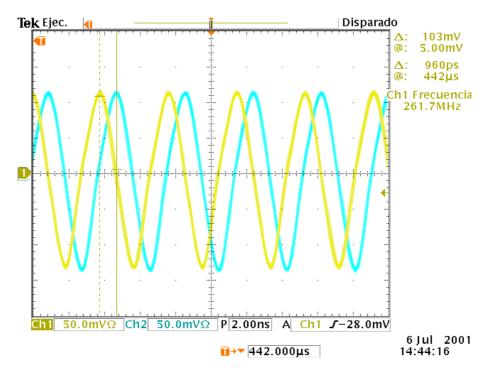

| 3.4          | Coupled oscillators                                       | 3-23 |

| 3.5 Design considerations for quadrature oscillators | 3-27 |

|------------------------------------------------------|------|

| 3.6 Quadrature oscillator design and test            | 3-32 |

| 3.7 Hybrid implementation of quadrature oscillators  | 3-35 |

| 3.8 References                                       | 3-39 |

| Chapter 4. Conclusions                               | 4-1  |

## Acknowledgments

Four years later, here we are. It has been a longtime since my advisor offered me the chance of pursuing a Ph.D. During this time, I asked myself several times why I decided to start and continue it. Research work is always interesting and attractive but it is also plenty of uncertainties: by definition you do not know where you will end up and the results you will get (but, this is exciting and challenging !!!!, isn't it?). Unfortunately, there are other uncertainties non-intrinsic to the Research you have to deal with (usually a low salary and its consequences, and sometimes time constants too long for a 4 year carriere). However, I suppose that Research is mainly a vocation (rather than a job) and you are ready to sacrifice or postpone some stuff in order to satisfy your curiosity and interests. In life, as in many problems in engineering, you have to find the better possible combination of tradeoffs for each particular situation/moment.

I must admit that sometimes it was hard to deal with these uncertainties of the student research life (even in spite of being a very convinced Ph.D. student). But the affection of your family and friends helps to overcome these bad (and few) moments. I know that it was also 'hard' for my parents. It is still difficult for me to explain to them what I did during my thesis and all the profits and good experiences I had during this time. Instead, they have seen a lot of work without an apparent reward other than a personal satisfaction. Despite, they always kept supporting and encouraging any decision I took. Now, it is done!!! and I specially want to dedicate this thesis to them. Thanks for your love, generosity and patience. Also to my sister and brother, who deserve a special recognition for everything they have generously and patiently managed in my absence all these years.

Starting a research trend is always a hard job. There is a lot of non- recognized work before getting any remarkable result. From these lines, I want to publicly recognize all the efforts of my advisor Prof. Jose Maria López-Villegas in building from scratch a RF research group in our lab. I would like also to thank him for sharing with me his expertise and for all our enjoyable scientific and non-scientific discussions. With him, you have the feeling of working with a colleague rather than with your 'boss'. Also, I

want to thank his generosity allowing and encouraging me to leave our lab and visit other labs (leaving behind me a lot of work to be done).

But there are other people in the RF group, Javier Sieiro, Aitor Osorio and J. Gabriel Macías. The success of this group has been not just being work colleagues but also good friends. I would like specially to mention Javier Sieiro. We started our Ph.D. together and for more than two years we have been working very closely until both of us visited foreign labs. During this time, we discussed our work almost in a daily basis and taught and helped each other (not just in our research work but also in our responsibilities as teaching assistants) and met together so many deadlines... Do you still remember ESSDERC 2000 and a poster arriving to the airport when I was in the boarding queue of a delayed plane? (I still get stressed just remembering it).

But the RF group is just a part very small of our lab. Many other people work here and set up an environment where it is nice to work in spite of our particular deadlines (conferences, projects, courses, etc) that sometimes make us to become almost crazy. I appreciate ALL my colleagues (professors or students) in the lab for creating a healthy and dynamic environment for conducting research. Also I want to thank all these people that in some way have done of our lab a place not just to work but also to have some fun. All these people who organized our soccer/basket matches, massive dinners or lunches, the famous 'calcotades' with the following soccer match or the paellas on the beach. All these events help you realize the excellent people you have around. I would like to thank all my professors for their help and friendship during all these years: Josep Ma. López-Villegas, Sebastia Bota, Manel Puig, Albert Cornet, Mauricio Moreno, Atilà Herms, Santiago Marco, José Bosch, Josep Samitier ..... And of course, I do not want to miss the chance to thank all my colleagues: Lourdes Cámara, Olga González, Judith Cerdà, Ana Ruiz, Stephanie Cheylan (who has read most of this thesis and corrected my English to make it understandable), Ana Vilà, Jaume López, Miguel Ángel Moruno, Pere Miribel, Toni Pardo, Teo Sundic, Alex Perera, Ángel Dieguez, Angel Cuadras, Jordi Puigcorbé, Jordi Arbiol, Flavio Hernández, Julio Duarte. And of course, I should not forget Rosa Ma, the always efficient secretary of the department.

And what about my office-mates (Enric Muntané, Manolo Carmona, Manel López, Nourdin) ??? Certainly, they did not like me very much since as soon as I arrived, many

of them decided to finish their Ph.D. Important decisions were taken in our office. Remember our coffee maker (specially addressed to Ph.D. students in the writing phase) that probably has been the precursor of the brand new coffee maker we have now in the lab. But if someone leaves, someone else comes. After they left some new students came (Cristina García, Rafael Ferrer). And they are so young that it tells you subtly that it is you the one who should leave now.

I would like to thank Professor Gabriel M. Rebeiz to welcome me in his group (the ticsg group: Laurent, Jeremy, Joe, Kiran, Jad, Abbas, Bernhard, Michael, Helena and many others) at the Radiation Laboratory of the University of Michigan (Ann Arbor) and for the excellent treatment I have received during all my time in AA. With no doubt, I found there not only excellent work colleagues but also excellent friends. I should specially mention Kiran Nimmagadda (the senior RFIC student at my arrival and already a doctor) who took me to his place during my first days in AA for as long as I was looking for a place of my own. He always demonstrated an amazing patience when I asked him for help (do you still remember your trip from San Diego to LA to solve some financial stuff?). I would also like to thank Jad Rizk for his friendship and support when I really needed it (gracias). Days are better if you start them with a good expresso coffee. I want to thank Helena for offering us every morning and afternoon our welcomed coffee and for the nice moments that many of the tixers spent having these coffees. I thank also Laurent Dussopt, my office-mate during most of my stay at the UoM, for the good company in our countless hours in the lab (remember Prof. Lievpa still thinks we were fighting for record of permanence in the lab) and for so many interesting discussions during our dinners in the cafeteria of the North Campus. And of course, I am not forgetting you Bernhard (the 'bavarian') and Abbas (Abbas, if you are reading this right now, I am sure it is at least 12 AM).

Also I would like to thank many other people in the RADLAB: Dejan Filipoulos, Marc Cachiatto, Dimitri Peroulis, Kailash Thaker (the RADLAB secretary-accountant), for all the nice dinners, theater movies we enjoyed during the weekend. All these good friends and nice people I have met in AA can explain the sadness I felt when I left (even considering it was –20 degrees which is a good enough reason to be very very happy to leave). AA would be a better place if it had a reasonable winter.

I am also grateful to Prof. Eugenio García and Miquel Roca of the University of Balearic Islands for their support and help in the application of some scolarships as well as to the Generalitat of Catalunya and to the 'Obra Social i Cultural de Sa Nostra' for the partial founding of my stay in AA.

And of course, let me finish (this is getting too long) by thanking Merce Deumal (Javier's wife) and Raimon Rubires for their friendship and support.

# INTRODUCTION

#### 1. Wireless World. Long and short range communications

The radio frequency and wireless market has suddenly expanded to unimaginable dimensions. Cellular phones, once considered yuppie toys or exotic extravagances have become indispensable items in our lives and work. Actually, by the time 2004 rolls by, there will be one billion mobile phone subscribers worldwide. Industry observers predict that by then the wireless phone population will equal —or exceed- that of wired phones [1], pointing out the fast penetration of the wireless technology in our society; much faster than other technologic advances such as the television or the wired phone.

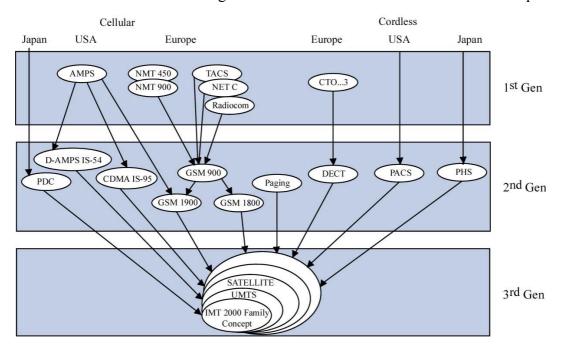

Figure 1. Evolution to the Third Generation<sup>1</sup>

1.

<sup>&</sup>lt;sup>1</sup>Data extracted from "Migration Paths 2G to 3G.Planning the Evolution to IMT 2000" by W. Groenen at ITU-D Seminar on IMT 2000, Warsaw, October 2001.

Nowadays, the second generation of mobile systems is consolidated. The GSM (Global System for Mobile Communications), probably the most successful 2G standard, provides digital wireless services (mainly digital telephony but also facsimile) to more than 721 million subscribers (end June 2002), accounting for approximately 71% of the wireless digital market today [2]. However, the existence of different standards in the USA, Japan and Europe as well as the low transmission data rate available (9.6 Kbits/s for GSM) suggest the need to evolve to a worldwide high-performance standard (UMTS, Universal) in the bosom of third generation of mobile communication systems (3G). The goal of this third generation is to deliver multimedia services to the user in the mobile domain. Thus, UMTS users will be provided with data rates up to 144 Kbits/s, 384 Kbits/s and 2 Mbits/s in macrocellular, microcellular and indoor environments respectively, enabling services such as real-time video (video-conferencing or video-telephony), mobile entertainment, etc [3].

Due to the endless possibilities of the UMTS and the enormous expectation seeded around it, the difficulties of the implementation of this technology were under-estimated and the initial planning for its progressive introduction had to be modified. At this time, Asian operators (Japan) are testing the waters with the first commercial 3G networks. In the United States, operators are still migrating away from TDMA technology as long as the European operators, struggling with high debt loads and a subscriber base nearing saturation, have postponed the introduction of the first UMTS services to the year 2003. However, in spite of the difficulties of the current situation, UMTS seems to be "inevitable" in the next future.

Along with mobile phones or pagers, where the distance between the emitter and the receiver can be very large, different applications with a much shorter range have also appeared. Between these short-range applications market, the wireless LAN's (WLAN) industry should be highlighted as one of the fastest-growing segments of the communication industry. Experts foresee the WLAN industry growing from the \$1.1 billion of 2000 to 5.2 billion by 2005, with significant growth beyond that [4]. Although, different standards for WLAN still exist in the marketplace, industry has converged on the standards sanctioned by the Wireless Ethernet Compatibility Alliance (WECA) based on the standard created by the 802.11 committee of the IEEE. These standards use modulations based on frequency-hopping spread spectrum around 2.4

GHz (Wi-Fi or IEEE802.11a) and 5 GHz (IEEE802.11a or HiperLAN2) with transmission speeds of 11 Mbps.

Another standard also intended for short-range communications (10-100m), is known as Bluetooth (named after Harald Blaatand "Bluetooth", king of Denmark 940-981). Invented by LM Ericsson in 1994 and followed by more than 1900 companies around the World (including Nokia, IBM, Intel, Motorola, Lucent, etc.), it operates in the unlicensed 2.4 GHz ISM band and allows transmission speeds of 780 Kbs/s [5,6]. Bluetooth attempts to provide a low cost (estimated around 5\$) method for short-range data communication between computers and their peripherals (file transfer, printing), but can also be useful for industrial automation or in domotic applications (heating or Hi-Fi systems, smart appliances, etc). Bluetooth is supposed to become a key technology as soon as very low cost transceivers are available.

#### 2. The Integrated RF Design. The RF Front-end

With this spectacular popularity of wireless communications (closely related to the advances in the IC technologies) and the increasing demand on communication portable systems of small size, low power, low cost and high performance, wireless architectures and circuit techniques have experienced a renaissance in the last decade. Once (and not so long ago), radio circuits were thought to be incompatible with the Silicon IC technologies, due to two main reasons:

- 1) The heavy reliance of RF integrated circuits (RFIC's) on tuned circuits and discrete filters (apparently, not suited to be integrated).

- 2) The limited bandwidth of the Silicon technologies.

Thus, for many decades the "RFIC" design was restricted to the GaAs technologies, due to the wide bandwidth of the MESFET GaAs transistors and to the high quality of the passive components. Inductors with relative high quality factors were affordable thanks to the insulating properties of the substrate and to the Au interconnections used typically in GaAs technologies [7,8]. This situation lasted until early 90's.

Then, as a result of technological improvements that increased noticeably the bipolar and specially the MOS transistors bandwidth (cut-off frequencies well above 30 and 50 GHz are found for CMOS and bipolar SiGe technologies respectively), the interest of Silicon integrated passive components was renewed. In 1990 Nguyen et al. published experimental measurements on integrated LC filters and inductors [9,10]. The quality factors reported ranged from 3 to 8, at frequencies above 1 GHz. Since then, huge efforts have been dedicated to improving the performance of the integrated inductors, resulting in quality factors close to 20 for bipolar processes using thick metal layers. Although these quality factors are still too low for some specific functions (as image or channel filters, or high Q resonators), they can be considered good enough for many other applications and as a consequence, can be included on-chip reducing the number of external components.

This relative youth of the RFIC design may help to explain that although today's pocket phones contain more than one million transistors (with only a very small fraction, often in the order of hundreds, operating in the RF range), the RF section is still the bottleneck of the complete system. In many applications, the front-end is still responsible for more than half of the power dissipation or the circuit area. Moreover, one of the largest and most expensive components in portable systems is often the battery. Since the total power consumption is dominated by the radio rather than by the digital circuits, the RF front-end also impacts the size and cost of the system through the battery size.

The difficulties involved in the RFIC design at current state-of-art may be summarized in three main categories:

1. **Technology related**. Digital circuits benefit directly from advances (scaling) in IC technologies since they can be translated almost directly to a newer process with the following reduction of the power consumption and area. Unfortunately, RF (analog) circuits involve many more design trade-offs in terms of gain, linearity, noise, power, etc (compared to the common trade-off speed-power consumption found in digital design) and hence do not benefit as much of the reduction of the transistor dimensions. Moreover, the large area of the passive components (mainly inductors) may prevent the area reduction associated to the technology scaling if they are included on a chip. Also,

the cross-talk across the substrate between the high speed digital circuits and the high-sensitive RF circuits represents an important challenge.

- 2. **Design tools related**. CAD tools for RF circuits are still in their infancy when compared with digital design tools, forcing the designer to rely on experience and intuition to predict the circuit performance. This increases the number of design cycles (design-fabrication-test) needed to obtain an optimum design. Related to the previous item, many digital processes are not accurately characterized for analog design. Thus, digital models can cause inaccuracies in the simulation results when the noise or non-linear characteristics of the designed circuit have to be predicted.

- 3. **System related**. RFIC design is a multi-disciplinar field that demands a solid understanding of many areas that are not related to integrated circuits such as microwave theory, communication theory, analog and digital modulation, transceivers architecture, etc. By example, the design of an LNA, a mixer or a PA depends strongly on the architecture in which it will be embedded and the type of modulation used. However, it is difficult for an IC designer to acquire the necessary knowledge of these disciplines in a short time. Therefore, traditional wireless system design has been performed at somewhat disjointed levels of abstraction: communication theoreticians create the modulation scheme and base-band signal processing, RF systems experts plan the transceiver architecture and IC designers develop the building blocks. In order to obtain an optimum system, it is essential the interaction and feedback between these different levels

In spite of the previous difficulties, an amazing progress has already been done towards the single-chip integration of the RF transceiver. Nevertheless, the ultimate goal of the Software Radio is still far [11]. In the Software Radio, the A/D conversion would take place at the carrier frequency, and from that moment on, any signal processing would be carried out at the digital level. The main advantage of this architecture would be its reconfiguration capability via software. Thus, the same equipment could work either as a cell phone using different bands and standards.

Nowadays, the requirements on the A/D converter (17-20 bits of resolution for 100dB dynamic range and 10 Gsamples/s sampling speed) and on the DSP speed (more than 10 GIPS) prevent the accomplishment of such an ideal architecture in the next future and

make it just a dream. However, the idea of moving the A/D closer to the antenna seems very promising.

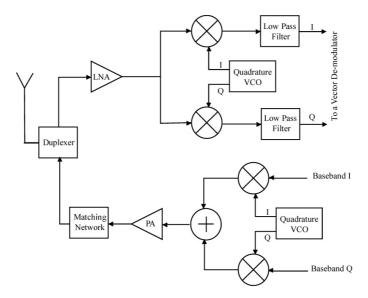

A much plausible goal in the short term consists in the integration on a single-chip of the transceiver and, specially, of the RF front-end, the part of the system responsible for providing gain (to convert weak signals to convenient amplitude levels for further processing) and frequency conversion. Figure 2 shows the typical structure of a RF front-end based on a direct conversion architecture where the different building blocks (Low Noise Amplifier, Mixer, Voltage-Controlled Oscillator, and Power Amplifier) can be identified.

Figure 2. Direct Conversion RF Front-end

Between these blocks, integrated CMOS LNA's [12,13,14] and mixers [15,16,17] with a good performance have already been reported and can be considered state-of-the-art. Conversely, the integration in CMOS processes of high performance VCO's and PA's able to satisfy the tight requirements imposed by the communication standards show considerable difficulties and is topic of active research.

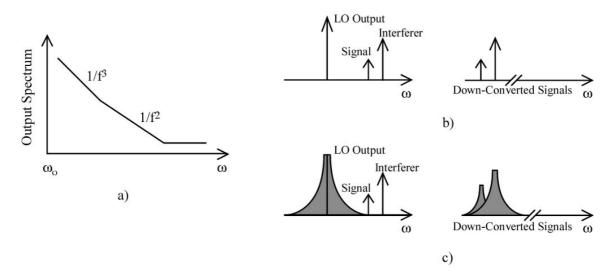

The fully integrated oscillators (and not exclusively CMOS) suffer from the relatively low quality factor of the integrated resonators, and in particular of integrated inductors, that limit the oscillator phase noise performance. A minor drawback, but also important, in the integration of VCO's consists in their limited tunning range.

The main difficulties associated to the PA are related to the high value of voltage needed to deliver a power in the order of watts to a  $50\Omega$  antenna while operating with low voltage supplies. Thus, due to the higher product of the cuttoff frequency and the breakdown voltage as well as to the high mobility and the high quality factor inductors, the power amplifiers still rely on the III-V technologies, particularly GaAs MESFETS and heterojunction bipolar transistors. However, recently SiGe technologies have also become an interesting alternative to the GaAs [18]. Unfortunately, it is not clear if submicron CMOS processes can achieve a similar performance, and at the moment, they are used basically for short-range applications or as pre-amplifiers [19].

Due to the intensive use of digital signal processing in modern transceivers as well as to the convenience of adding digital blocks into the front-end for frequency synthesis, adaptability, multi-mode operation and sophisticated detection, a single-chip solution has to be implemented using a CMOS technology or any of its variants (such as the Silicon-on-Insulator (SOI) CMOS, BiCMOS or the SiGe BiCMOS). This raises questions such as how well digital CMOS circuits can co-exist on the same substrate as the radio front-end, or whether there is sufficient on-chip isolation in a low cost package to guarantee stable operation of a receiver with more than 100 dB of base-band gain, or how the power amplifier modulates the on-chip local oscillator. The future of single chip CMOS transceivers may well depend on the satisfactory answers to these questions, and will demand technological improvements along with circuit and architecture design techniques that take advantage of the strengths of CMOS, and circumvent its weakness. Next section is dedicated to the direct conversion architecture that nowadays is playing a key role in the way towards this integration.

#### 3. RF Architectures. Direct Conversion

In the previous section, we have mentioned the different levels of abstraction involved in the RFIC design. Thus, parameters as the gain, the noise figure or the third-order intercept point used at the circuit level to specify the properties of different building blocks of a RF front-end, increase their meaning when considered in a higher abstraction level, that is, the system level.

Let us illustrate this situation with an example: connect in cascade a LNA and a matched mixer characterized by their respective noise figures  $NF_{LNA}$ ,  $NF_{mix}$  and gains  $A_{LNA}$ ,  $A_{mix}$ . The resulting noise figure for the cascaded system  $NF_{tot}$  is given by:

$$NF_{tot} = NF_{LNA} + \frac{NF_{mix} - 1}{A_{LNA}^2}$$

This expression shows that the resulting noise figure depends mainly on the LNA noise figure for the common values of gain found in LNA's. A reversed expression would be found if the mixer and the LNA interchange their positions, pointing out that the properties of the system depend strongly not just on the specific properties of its building blocks but also on their proper connectivity, that is, on the system architecture.

Complexity, cost, power dissipation and the number of external components have been the primary criteria in selecting the transceiver architecture. However, as the IC technologies evolve embracing more parts of RF systems, the relative importance of each of these criteria changes, and transceiver architectures as the direct conversion architecture that once seemed impractical may return as plausible solutions.

The direct conversion or homodyne architecture, invented many decades ago, has recently become the topic of active research again [20,21,22]. In spite of being the natural or intuitive approach for the receiver architecture, its implementation was tried many times, and failed almost every time, justifying thus the omnipresence in the practical implementations of the super-heterodyne receivers. Nowadays, several reasons account for this renewed interest:

- 1. Direct conversion, in principle, lends itself to monolithic integration much more easily than do heterodyne receivers and would result in systems with smaller size, weight and power consumption.

- Direct conversion past failures were due primarily to effects (offsets, mismatches, etc) that could not be removed in discrete implementations, but may be controlled or suppressed in integrated circuits.

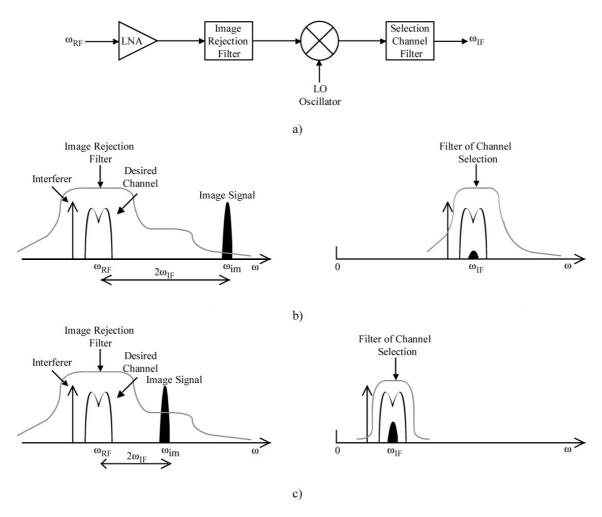

In order to appreciate why DCR's are amenable for integrated implementations, let us briefly review the heterodyne receiver shown in fig.3a where the RF input signal is firstly amplified by a low-noise amplifier and subsequently filtered by an image reject filter [20]. The result is then mixed with a local oscillator, producing the intermediate frequency IF signal where the out-of-channel interferers are suppressed by the IF filter.

Figure 3. a) The super-heterodyne receiver. b) High IF frequencies favours the rejection of the image frequency c) Low IF frequencies favours the rejection of near interferers

The main issue in the heterodyne architecture consists in the trade-off between adjacent channel suppression and image rejection. Thus, taking into account that Q relates the filter bandwidth  $\Delta f$  with its central frequency  $f_c$ ,  $Q = \frac{f_c}{\Delta f}$ , the lower is the IF frequency,

the most suppressed are the interferers (if a constant quality factor is assumed for the channel filter). However, lowering the IF frequency results in a significant corruption of the down-converted signal associated to the frequency image. Conversely, if the IF is high, the image is greatly attenuated whereas nearby interferers remain at significant levels, as shown in fig. 3c. For this reason, both the image rejection filter and the IF channel filter require highly selective transfer functions that are impractical in today's

IC technologies. The solution has been to employ external bulky filters such as surface acoustic wave (SAW) devices, limiting seriously the integration of the receiver.

Another drawback of heterodyne receivers is that the LNA must drive a 50 ohms load because the image rejection filter is placed off chip. This adds an additional constraint to the LNA design and establishes another dimension to the trade-offs among noise, linearity, gain and power dissipation of the amplifier.

Direct conversion receivers translate the band of interest directly to zero frequency (that is why they are also called zero-IF receivers), circumventing the problem of the image frequency and removing the necessity of the IF SAW filters. Instead, the nearby interferers are suppressed using low pass high-order active filters and base-band amplifiers that are amenable of monolithic integration and have very low power consumption since they operate at very low frequencies. Moreover, the LNA does not need to drive a 50 ohms load, because no image filter is required.

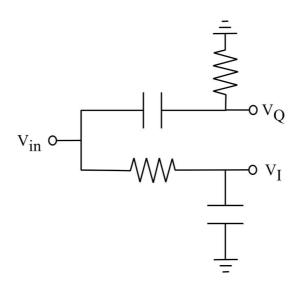

The direct conversion architecture requires quadrature channels (I-Q) for vector modulation and demodulation since each sideband of the RF spectrum contains different information and would result in irreversible corruption if they overlap each other without being separated properly (as shown in fig. 2). Whereas in superheterodyne receivers, the quadrature down-conversion is performed at the second LO frequency, in direct conversion receivers this has to be done at the much higher carrier frequency. Thus, it is a great challenge to produce quadrature phases with good amplitude match at RF frequencies. In case of double-sideband signals no quadrature signals are needed and a simpler receiver can be used (fig.4). Nevertheless, double sideband modulations are not employed in practice due to their inefficient bandwidth use.

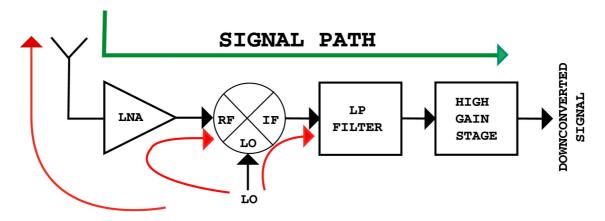

In spite of its apparent simplicity, direct conversion entails a number of issues that do not exist or are not serious in a heterodyne receiver and have prevented the proliferation of successful implementations [20]. Since in the direct conversion architecture the down-converted band extends to zero frequency, any dc offset voltages can corrupt the signal and, more importantly, saturate the following stages. To understand the origin and impact of these offsets, consider the simple receiver shown in fig.4 and let us analyze how the finite isolation of the mixer affects the performance of the receiver.

Figure 4. "Self-Mixing" and "LO leakage" in Direct Conversion Receivers

The isolation between the LO port and the inputs of the mixer and the LNA is not perfect (common values for the mixer LO-IF isolation are around 40 dB), i.e., a finite amount of feed-through exists from the LO port to the input and output of the LNA. Called "LO leakage" this effect arises from the capacitive and substrate coupling and, if the LO signal is provided externally, bond-wire coupling. Mixer mismatches are also responsible for this finite isolation. Then, the leakage signal appearing at the inputs of the LNA and the mixer is mixed with the LO signal, thus producing at the IF port a dc component that overlaps with the down-converted signal. This phenomenon is called self-mixing.

A similar effect occurs if a large interferer leaks from the LNA or the mixer input to the LO port and is multiplied by itself. The problem of offset is even exacerbated if the self-mixing varies with time, as it occurs if the leaked LO signal is radiated by the antenna and then reflected back to the receiver or in frequency hopping receivers. Different techniques as AC coupling, offset cancellation schemes or use modulations with negligible energy below few kilohertz can be applied to alleviate the offset problems [20,24,25].

Along with the dc offsets, the direct conversion architecture suffers from some additional drawbacks [26]:

1) I-Q accuracy. Phase and amplitude imbalances in the I-Q channels can corrupt the down-converted signal, thereby raising the bit error rate. The problem of the I-Q

mismatch has been a major obstacle in discrete designs, but it tends to decrease with higher levels of integration.

- 2) Even-order distortion. Typical RF receivers are susceptible only to odd-order intermodulation effects, but in direct conversion receivers, even-order distortions become also problematic. Thus, if two strong interferers of frequencies  $\omega_1$  and  $\omega_2$  close to the channel of interest experience a second order nonlinearity (in the LNA or the mixer), a low frequency term  $\omega_1$ - $\omega_2$  will appear at the receiver output associated to the finite isolation and mismatches in the mixer.

- 3) Flicker noise. Due to the extremely low power of the RF signal, the down-converted signal is very small and quite sensitive to noise. Thus, the low frequency amplifiers have to be designed carefully to minimize the influence of flicker noise of the devices, especially in MOS implementations.

- 4) Local Leakage. Apart from creating serious offset problems, the LO signal may leak through the antenna in spite of the reverse isolation of the mixer and the LNA and generate in band interferences to other close receivers. The regulatory bodies and wireless standards limit the level of this LO leakage.

In spite of these drawbacks, direct conversion seems to be the most suitable solution in the next future for the implementation of portable, low power RF front-ends and some functional designs have been already reported [27].

#### 4. Future trends

Despite a general optimistic landscape, we do still have many uncertainties in our way towards the fully integrated wireless systems. Although the SiGe and SOI technologies will be available, we can wonder ourselves if their cost will match the requirements of BiCMOS RF-Analog-Digital radio integration in the next few years? Are these or other technologies the right ones indeed? If we consider that the ultimate goal in the design of wireless systems would be to combine the RF front-end and the base-band processors in a single-chip low cost solution, many problems still remain to be solved (specially, for high performance applications):

- 1. The signal-to-noise ratio of the analog blocks can be degraded by the digital (noisy) parts due to the coupling via the substrate or the power lines.

- 2. Analog circuit and especially RF circuits have a lower yield than digital circuits due to the inevitable parametric variations, reducing the yield of a monolithic implementation of the overall system.

- 3. An important percentage of the area of the RF circuits (around 60%) is dedicated to passive components, mainly inductors. Unfortunately, the performance of these passive components built on a standard IC process is relatively low and have a direct effect on the system performance (power consumption, noise figure, phase-noise, etc). Moreover, the area of the passive components does not decrease with the technology scaling, increasing the cost of these integrated components.

- 4. Some blocks, as the power amplifier with high output power or the antenna switch, suffer an important performance penalty if they are implemented in CMOS processes compared to their bipolar or GaAs counterparts, decreasing the performance of a whole system implemented in a pure CMOS process.

Moreover the realization of a single chip RF transceiver should not just be technically feasible, but also cost effective. Recently, the cost reduction of high performance systems (and not exclusively wireless systems) has raised a noticeable interest in a new design philosophy known as system on a package (SOP) as alternative to the single chip approach [28-29].

In this technology, several components or circuits can be each implemented in the most suitable (in terms of cost or performance) IC technology and then assembled together in a common 'substrate' (carrier substrate) by using a Muti-Chip Module (MCM) technology. This interconnection technology is relatively simple and economical and consists in alternating layers of low k dielectrics and low resistivity metal layers (copper) on a carrier substrate as diverse as high resistivity silicon, glass or low loss ceramics. In some way, this process can be seen as a 'high performance PCB process' (still done in a clean room) and allows heterogeneous devices/circuits to be integrated into a small form factor.

As an example, in a RF front-end the PA or the antenna duplexer/switch could be implemented in a GaAs process as long as a cheaper BiCMOS technology would be

used for the rest of the circuit. A similar system-partitioning could be done in digital circuits where the technologies used in memories are considerably cheaper than the ones used for processors or ASIC's. The system partitioning also allows the revision of each IC without being forced to upgrade the complete system, increasing the design flexibility.

In addition to matching the circuit functionality and performance to the best technology available in terms of cost, the SOP offers more advantages. In particular, the MCM interconnection technology (with copper and low k dielectrics) can be used to implement wide bandwidth I/O busses between high-speed digital circuits that are difficult to implement between packaged circuits [30-31]. This interconnection process can also be used in RF applications to obtain high quality and low cost passive components (not just inductors, but also filters, MEMS switches or varactors and even antennas), since they are built on a low loss and low cost substrate. Additional benefits of this approach consist in an improved isolation between the different IC's; thus low cost digital and high performance analog circuitry can share the same package, thereby retaining a high level of integration as well as a good relation cost, performance and functionality [32,33,34].

#### 5. Organization and Goals of this Thesis

In this Introduction we have performed a top-down description of the environment around the wireless communications, mainly addressed to the design of RF circuits and the issues related to the fully integration of a RF front-end such as circuit architecture or available technologies. Eventually the complete RF transceiver has also been considered. The required coexistence of digital blocks and the analog-RF circuitry in modern transceivers sets the CMOS (or some of their variants such as the BiCMOS) as the only suitable technology for this monolithic implementation.

The direct-conversion architecture also plays a key role in this way towards the monolithic integration of wireless systems since it solves the problem of the IF image signal of super-heterodyne receivers and removes the necessity of the (non-integrable) image rejection filters. Unfortunately, the direct conversion architecture also comes with

some new issues that either did not exist or were not as relevant in the classical superheterodyne architecture. The generation of quadrature signals at RF frequencies as high as 5 GHz, or the dc offsets and the self-mixing that can saturate the high gain amplifiers of the signal path are some of the most important.

The context of this thesis is the design of CMOS low power RFIC's suitable for direct conversion architectures. Our starting point is the analysis of the characteristics of the integrated passive components (inductors and mainly transformers) from a circuit designer perspective. Then, the achieved understanding of these components is exploited in order to optimize the performance of some of the building blocks of a RF front-end.

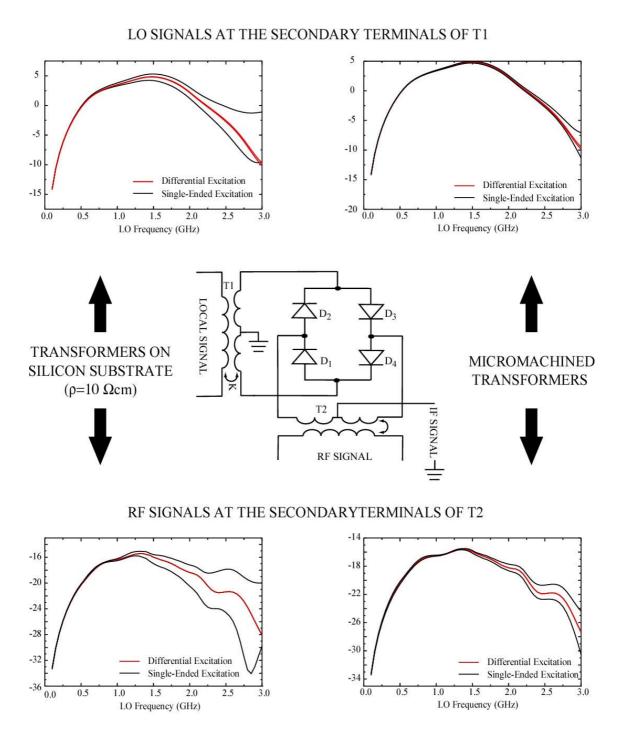

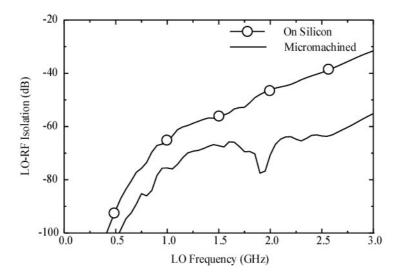

This thesis is divided in three main chapters. Chapter 1 is dedicated to the analysis of integrated transformers. It starts with a revision of the state of the art of the integrated inductors in order to set up the basis for the analysis of the monolithic transformers. Due to their influence on the component quality factor, a special insight is dedicated to the analysis of the eddy currents. Then, we introduce the integrated transformers and revise the topologies used in their implementation and their characteristics and electrical equivalent models. However, it is important to remark that the goal of this thesis is not the modeling of the component. Instead, we will use EM simulators to reproduce their behavior and point out some physical mechanisms present in integrated transformers that have not been properly considered in the equivalent electrical models presented in the literature so far. In particular, we will study eddy currents in integrated transformers and will demonstrate their dependence on the operating mode of the transformer as well as on the loads connected to the primary and the secondary. As we will see this phenomenon has a direct influence on the component model as well as on the component optimization. Thus, different optimization procedures should be applied to minimize the component losses depending on the application.

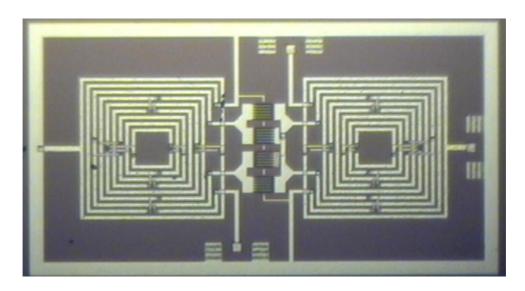

Finally, this chapter finishes with the design of a double balanced mixed that uses two differential transformers to increase the isolation between ports. It is demonstrated that a differential driving minimizes the effects of the parasitic capacitances and increases noticeably this isolation. It is also shown that the etching of the silicon underneath of

the integrated transformers that reduces these parasitic capacitances also increases this isolation (even if a single-ended excitation is applied).

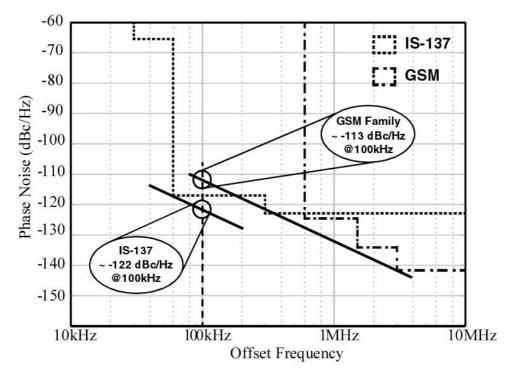

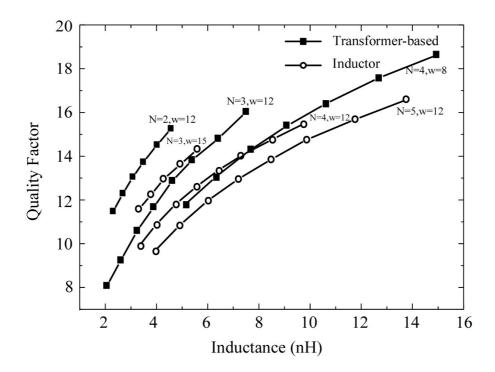

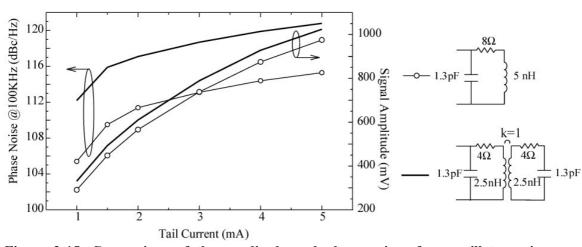

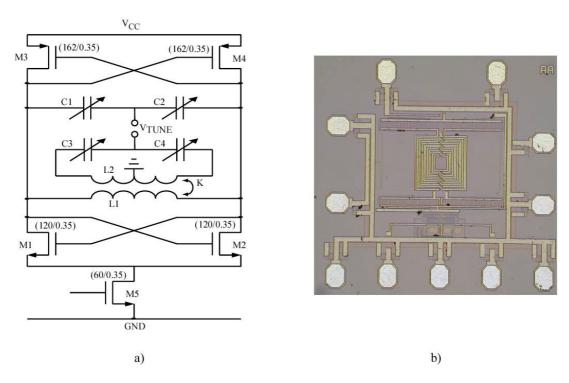

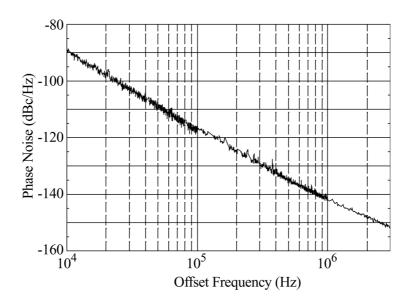

Chapter 2 investigates the design of oscillators having low phase noise and large tunning range. After identifying the quality factor of the integrated inductors as one of the main factors limiting the oscillator phase noise, a novel transformer-based (parallel) resonator is introduced. This new topology overcomes the performance of the common inductor-based resonators in terms of tuning range and effective quality factor.

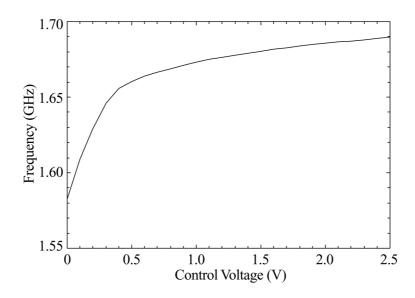

A detailed description of the resonator is then performed in order understand its potentially and limitations. Thus, its properties are firstly studied from an electrical circuit perspective using the equivalent models discussed in the previous chapter. Then, it is realized the analysis in the EM domain in order to compare its performance with the standard inductor-based resonator. Once again, eddy currents are identified as the main factor limiting the effective quality factor of the transformer-based resonator. Thanks to the already achieved understanding of integrated transformers, the layout optimization method proposed by López-Villegas [35] for integrated inductors can be extended to the optimization of the transformer (when working in common-mode). The extension of the parallel design to N-resonators is also shortly discussed. Finally, the proposed resonator is used in a low phase-noise 1.7 GHz CMOS VCO.

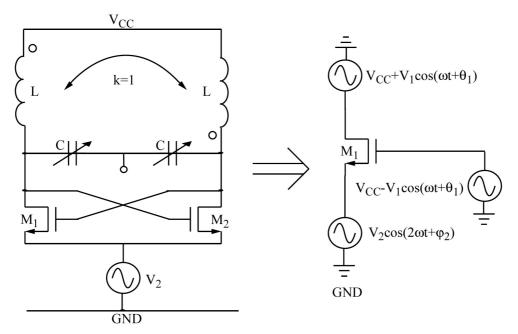

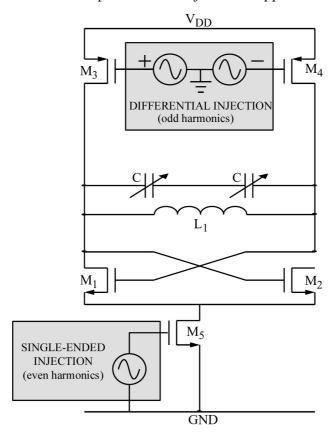

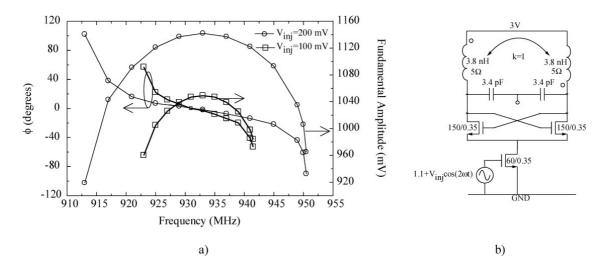

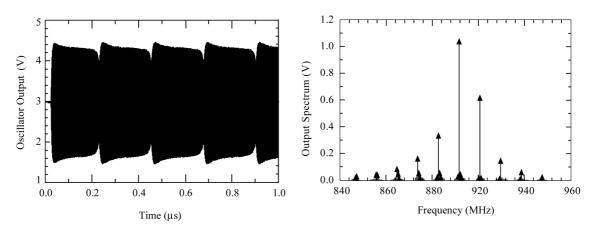

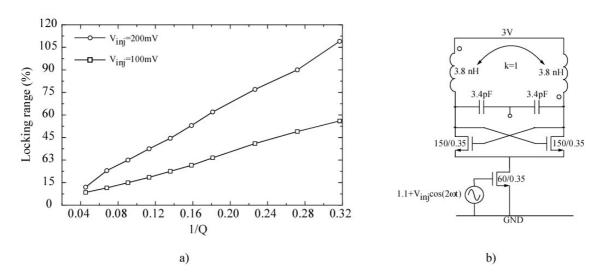

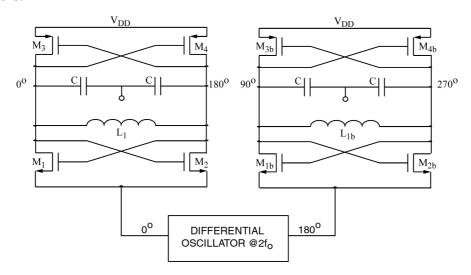

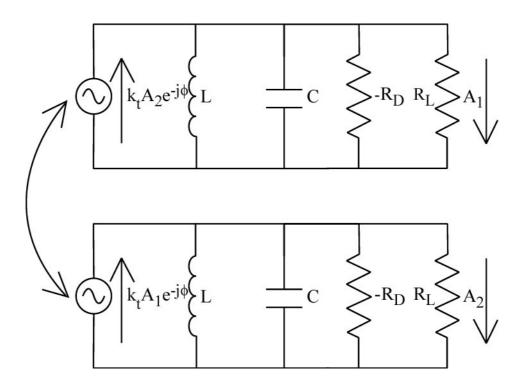

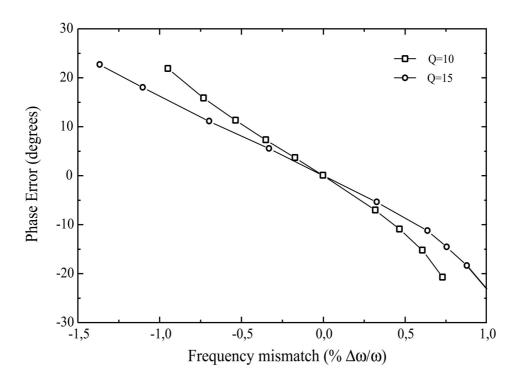

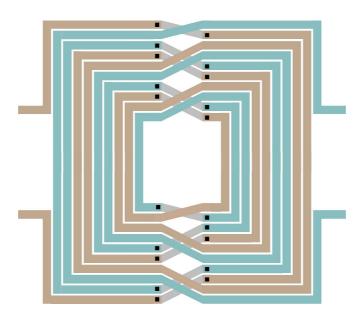

Chapter 3 presents a new topology of quadrature oscillator based on the differential coupling at the second harmonic of two differential oscillators. As in the previous design, an integrated transformer plays a relevant role in this circuit being used to establish the coupling between oscillators. In order to obtain a basic understanding of the phenomena involved in the generation of quadrature signals using the proposed method and set up the design procedure several concepts must be revised. In particular, the theory on forced (or injected) and coupled oscillators is discussed and applied to the proposed quadrature oscillator. Finally, to show the feasibility and potentiality of this methodology, different designs in integrated and hybrid implementations are presented.

#### 6. References

- [1] E. Rejman, "3G is poised to take over the cellular World", Microwave Journal, pp.162-171, Sept. 1999

- [2] http://www.gsmworld.com.

- [3] Richardson, K.W. "UMTS overview", Electronics & Communication Engineering Journal, Vol. 12 Issue: 3, pp. 93 –100, June 2000.

- [4] J.Abramowitz, "Wireless LANs-Poised for Untethered Growth", 2001. <a href="http://www.WLANA.org">http://www.WLANA.org</a>.

- [5] Wei-Shin Wang, "Bluetooth: A new era of connectivity", IEEE Microwave Magazine, Vol. 3 Issue: 3, pp. 38 –42, Sept. 2002

- [6] Sairam, K.V.S.S.S.S.; Gunasekaran, N.; Redd, S.R.,"Bluetooth in wireless communication" IEEE Communications Magazine, Vol. 40 Issue: 6, pp. 90 –96, June 2002

- [7] Geen, M.W.; Green, G.J.; Arnold, R.G.; Jenkins, J.A.; Jansen, R.H. "Miniature multilayer spiral inductors for GaAs MMICs", Gallium Arsenide Integrated Circuit (GaAs IC) Symposium, 1989. Technical Digest 1989, 11th Annual, pp. 303–306, 1989

- [8] Bahl, I.J. "Improved quality factor spiral inductors on GaAs substrates", IEEE Microwave and Guided Wave Letters, Vol. 9 Issue: 10, pp. 398 –400, Oct. 1999

- [9] Nguyen, N.M.; Meyer, R.G., "Si IC-compatible inductors and LC passive filters", Solid-State Circuits, IEEE Journal of, Vol. 25 Issue: 4, pp. 1028 –1031, Aug. 1990

- [10] Chang, J.Y.-C.; Abidi, A.A.; Gaitan, M., "Large suspended inductors on silicon and their use in a 2-µm CMOS RF amplifier", IEEE Electron Device Letters, Vol. 14 Issue: 5, pp. 246–248, May 1993

- [11] Buracchini, E., "The software radio concept", IEEE Communications Magazine, Vol. 38 Issue: 9, pp. 138 –143, Sept. 2000

- [12] Leroux, P.; Janssens, J.; Steyaert, M., "A 0.8-dB NF ESD-Protected 9-mW CMOS LNA operating at 1.23 GHz [for GPS receiver]", Solid-State Circuits, IEEE Journal of, Vol. 37 Issue: 6, pp. 760 –765, June 2002

- [13] Gatta, F.; Sacchi, E.; Svelto, F.; Vilmercati, P.; Castello, R., "A 2-dB noise figure 900-MHz differential CMOS LNA", Solid-State Circuits, IEEE Journal of, Vol. 36 Issue: 10, pp. 1444 –1452, Oct. 2001

- [14] Yongwang Ding; Harjani, R., "A +18 dBm IIP3 LNA in 0.35 /spl mu/m CMOS", Solid-State Circuits Conference, 2001. Digest of Technical Papers. ISSCC. 2001 IEEE International, pp. 162-163, 443, 2001

- [15] Behbahani, F.; Kishigami, Y.; Leete, J.; Abidi, A.A., "CMOS mixers and polyphase filters for large image rejection", Solid-State Circuits, IEEE Journal of, Vol. 36 Issue: 6, pp. 873–887, June 2001

- [16] Umeda, T.; Otaka, S.; Kojima, K.; Itakura, T., "A 1 V 2 GHz CMOS up-converter using self-switching mixers", Solid-State Circuits Conference, 2002. Digest of Technical Papers. ISSCC. 2002 IEEE International, Vol. 1, pp. 402 –476, 2002

- [17] Weldon, J.A.; Narayanaswami, R.S.; Rudell, J.C.; Li Lin; Otsuka, M.; Dedieu, S.; Luns Tee; King-Chun Tsai; Cheol-Woong Lee; Gray, P.R., "A 1.75-GHz highly integrated narrow-band CMOS transmitter with harmonic-rejection mixers", Solid-State Circuits, IEEE Journal of, Vol. 36 Issue: 12, pp. 2003 –2015, Dec. 2001

- [18] Pei-Der Tseng; Liyang Zhang; Guang-Bo Gao; Chang, M.F., "A 3-V monolithic SiGe HBT power amplifier for dual-mode (CDMA/AMPS) cellular handset applications", Solid-State Circuits, IEEE Journal of , Vol. 35 Issue: 9, pp. 1338 1344,Sept. 2000

- [19] Gupta, R.; Ballweber, B.M.; Allstot, D.J., "Design and optimization of CMOS RF power amplifiers", Solid-State Circuits, IEEE Journal of, Vol. 36 Issue: 2, pp. 166–175, Feb. 2001

- [20] Razavi, B., "Design considerations for direct-conversion receivers", Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on, Vol. 44 Issue: 6, pp. 428–435, June 1997

- [21] Abidi, A.A., "Direct-conversion radio transceivers for digital communications", Solid-State Circuits, IEEE Journal of, Vol. 30 Issue: 12, pp. 1399 –1410, Dec. 1995

- [22] Abidi, A.A., "Direct-conversion radio transceivers for digital communications", Solid-State Circuits Conference, 1995. Digest of Technical Papers. 41st ISSCC, 1995 IEEE International, pp. 186-187, 363-4, 1995

- [23] B. Razavi, "RF Microelectronics" Prentice Hall PTR, ISBN: 0138875715, 1<sup>st</sup> ed., Nov. 1997.

- [24] Matinpour, B.; Chakraborty, S.; Laskar, J., "Novel DC-offset cancellation techniques for even-harmonic direct conversion receivers", Microwave Theory and Techniques, IEEE Transactions on, Vol. 48 Issue: 12, pp. 2554-2559, Dec. 2000

- [25] Zhaofeng Zhang; Zhiheng Chen; Tsui, L.; Lau, J., "A 930 MHz CMOS DC-offset-free direct-conversion 4-FSK receiver", Solid-State Circuits Conference, 2001. Digest of Technical Papers. ISSCC. 2001 IEEE International, pp. 290-291, 456, 2001

- [26] Razavi, B., "Challenges in portable RF transceiver design", IEEE Circuits and Devices Magazine, Vol. 12 Issue: 5, pp. 12 –25, Sept. 1996

- [27] Ali, F., "Direct conversion receiver design for mobile phone systems challenges, status and trends", Radio Frequency Integrated Circuits (RFIC) Symposium, 2002 IEEE, pp. 21 –22, 2002

- [28] Tai, K.L., "System-In-Package (SIP): challenges and opportunities", Design Automation Conference, 2000. Proceedings of the ASP-DAC 2000. Asia and South Pacific, pp. 191–196, 2000

- [29] Tummala, R.R.; Madisetti, V.K., "System on chip or system on package?", IEEE Design & Test of Computers, Vol. 16 Issue: 2, pp. 48 –56, April-June 1999

- [30] Goetz, M., "System on chip design methodology applied to system in package architecture", Electronic Components and Technology Conference, 2002. Proceedings. 52nd, pp. 254–258, 2002

- [31] Sundaram, V.; Fuhan Liu; Dalmia, S.; Hobbs, J.; Matoglu, E.; Davis, M.; Nonaka, T.; Laskar, J.; Swaminathan, M.; White, G.E.; Tummala, R.R., "Digital and RF integration in system-on-a-package (SOP)", Electronic Components and Technology Conference, 2002. Proceedings. 52nd, pp.646–650, 2002

- [32] Kyutae Lim; Pinel, S.; Davis, M.; Sutono, A.; Chang-Ho Lee; Deukhyoun Heo; Obatoynbo, A.; Laskar, J.; Tantzeris, E.M.; Tummala, R., "RF-system-on-package (SOP) for wireless communications", IEEE Microwave Magazine, Vol. 3 Issue: 1, pp. 88–99, March 2002

- [33] Chakraborty, S.; Lim, K.; Sutono, A.; Chen, E.; Yoo, S.; Obatoyinbo, A.; Yoon, S.-W.; Maeng, M.; Davis, M.F.; Pinel, S.; Laskar, J. "A 2.4-GHz radio front end in RF system-on-package technology", IEEE Microwave Magazine, Vol. 3 Issue: 2, pp. 94 104, June 2002

- [34] Wambacq, P.; Donnay, S.; Ziad, H.; Engels, M.; De Man, H.; Bolsens, I., "A single-package solution for wireless transceivers", Design, Automation and Test in Europe Conference and Exhibition 1999. Proceedings, pp. 425–429, 1999

- [35] López-Villegas, J.M.; Samitier, J.; Cane, C.; Losantos, P.; Bausells, J. "Improvement of the quality factor of RF integrated inductors by layout optimization" Microwave Theory and Techniques, IEEE Transactions on, Vol. 48, pp. 76 –83, Jan. 2000

# INTEGRATED TRANSFORMERS

#### Introduction

Since Nguyen and Meyer demonstrated the feasibility of integrated inductors on Silicon substrates, huge research efforts have been dedicated to their analysis, design, modelling and optimization. The hundreds of papers dealing with integrated inductors published in specialised journals during the last ten years corroborate this fact. As a result of these efforts, the inductor performance has been noticeably improved. Conversely, integrated transformers still remain strange components and are rarely used.

In this chapter we will analyze the integrated or monolithic transformers and we will try to set up a fundamental understanding of their properties. This knowledge will prove very useful to guide the circuit designer towards an efficient/optimum design of these components and help him to fully exploit their potential or skip their limitations.

Since a transformer is nothing else than two coupled inductors, a solid knowledge of the characteristics and limitations of the integrated inductors will be an excellent starting point for the analysis of integrated transformers. Therefore, this chapter starts with a short revision of the state-of-the-art of the integrated inductors, pointing out how the technology affects their performance and in particular, their quality factors.

Reproducing a lumped equivalent electric model for an integrated inductor, commonly found in the literature and based on physical assumptions, the improvements achieved by the technological advances can be easily understood. Many times this equivalent model is the only tool available for the circuit designer and the lack of an additional comprehension of the component characteristics leads to an inefficient or non-optimum use of it.

In spite of the many similarities between inductors and transformers, there are some important differences in how magnetically induced losses affect these components and are considered in their equivalent models. Thus, during the inductor revision, special attention is given to the analysis (based on EM simulators) of the different mechanisms that contribute to inductor losses (i.e. limit their quality factor) for a further comparison. The transcendence of the quality factor from the circuit point of view is widely discussed in Chapter 2.

Later, the ideal transformer is presented and the different topologies used to implement integrated transformers are compared. The transformer equivalent model is shortly discussed since the modeling of the component is out of the scope of this work. However, some important facts that affect directly the modeling of the component are pointed out for the first time. In particular, in this work we will demonstrate that the transformer losses can not be reproduced with the transformer models proposed so far. Moreover, the understanding of the transformer losses will point out that the optimization of the transformer layout is strongly dependent on the application.

Finally, this chapter finishes with the design of a double balanced mixer that uses two differential transformers to increase the isolation between ports. It is demonstrated that a differential driving reduces the effects of the parasitic capacitances and increases noticeably the LO-RF isolation, a key parameter when the mixer is intended for direct conversion since it minimizes the self-mixing. It is also shown that the etching of the silicon underneath the integrated transformers which, decreases these parasitic capacitances also increases this isolation (even when a single-ended excitation is applied).

#### 1.1 Integrated Inductors

Basically, two parameters, the self-resonant frequency and the quality factor characterize the performance of any inductor. The self-resonant frequency (SRF) is caused by the parasitic capacitances and offers an estimation of the maximum operating frequency of the component. For frequencies above the SRF the inductor shows a negative reactance, i.e. acts like a capacitor.

The quality factor is defined as the ratio between the magnetic power stored and the power dissipated in the component. Thus, the higher the quality factor, the smaller the power lost in the component. For an inductor, the previous definition of Q results in  $Q=\omega L/r_s$  where L is the inductance value and  $r_s$  is the series resistance associated to the metal strips. It is also quite common to define the quality factor of a resonator in terms of the phase of the impedance  $\theta$  as:

$$Q = -\frac{\omega_o}{2} \frac{d\theta}{d\omega}\bigg|_{\omega = \omega_o} \tag{1.1}$$

being  $\omega_0 = 2\pi f_0$ , with  $f_0$  the resonant frequency.

For a simple LC resonator, built with a lossless capacitor both definitions of Q are equivalent.

High Q inductors can be used in LNA's [1,2] as passive loads to increase their gain (gain peaking) or as matching elements to reduce its noise figure [3]. In Gilbert cell mixers [4], inductors can be used as degeneration elements to increase the circuit linearity. High Q inductors also improve the phase noise performance of oscillators and reduce their power consumption [5,6]. Moreover, when inductors are used as passive loads or as degeneration elements, it allows the reduction of the dc voltage headroom since no dc voltage appears across them. In summary, the benefits of high Q values translate directly to low-noise and low-power systems.

To understand the limited performance of the integrated inductors, the characteristics of the technologies used in their implementation and their evolution must be revised. Besides, this technological review may allow us to predict future trends in their implementation or how new technology advances will affect their performance.

#### 1.1.1 Silicon Technologies for RF Applications

In the early 60's, the first studies about passive components integrated on Silicon substrates realized by Warner and Fordemwalt led to the conclusion that their performance would be limited even for HF frequencies [7]. Low self-resonant frequencies and high losses were the unwanted but actual characteristics of Silicon integrated inductors.

The overall inductor losses can be divided into two main contributions: substrate losses and strip metal losses. Due to the low resistivity of the Silicon substrates (and specially, of the substrates used in CMOS processes) and to capacitive coupling, conduction currents flow not only along the metal strips but also in the silicon substrate. Besides, the magnetic field generated by the inductors may also induce currents in the low resistivity substrate. The losses caused by both current contributions impact dramatically on the component performance.

The substrate losses can be minimized or even removed placing an insulator in the local area underneath the inductor. Actually, the best solution would consist in the complete removal of the substrate underneath the component. This can be easily accomplished using bulk or surface silicon micromachining [8,9] and yields clear advantages:

- 1) The self-resonant frequency is shifted up.

- 2) Substrate losses are completely removed.

However, this method, applied by Chang et al. [9] to the design of a CMOS RF amplifier in the early 90's, has not been well received by the industry. The reasons are the necessity of a post-processing step to remove the substrate and mainly the possibility of mechanical failure of the device during the packaging process.

A more conservative approach to improve the inductor performance, but still in the same direction, consists in placing the device on an insulating substrate such as quartz [10,11], sapphire [12,13], glass [14,15] or high-resistivity silicon [16]. When comparing this technique to the micromachining, the main advantage is the presence of mechanical robustness. However, self-resonance is decreased due to the higher permittivity of these materials.

An additional source of losses in integrated inductors arises from the strip resistance due to the thin metal layers of aluminium typically used in digital IC processes. These losses are still more evident if either of the techniques described previously is employed. Losses in the metal regions are mainly related to the metal strip resistance (sheet resistance) and their analysis requires taking into account conduction (ohmic) losses and magnetically induced losses (related to eddy currents). Actually, at the end of this section, a detailed analysis of these magnetically induced losses is performed. Several techniques can be introduced to decrease the value of this sheet resistance:

- 1) Increase the metal thickness or use stacked metal layers [17].

- 2) Use metals with lower resistivity (Cu instead of Al) [16,18].

Nowadays, most of the commercial analog high performance processes still do not exploit fully the above mentioned techniques. In most of the cases, an additional module is added to the basic process to obtain high Q inductors. This additional module consists in a thick metal layer (around 3  $\mu$ m) on top of a thick dielectric layer to separate the spiral from a relatively high resistivity substrate.

Currently, for short channel digital technologies, the interconnection delay is becoming comparable to the gate delay, and affecting seriously the circuit speed [20]. To solve this issue digital technologies are moving to other types of metals (in particular copper) and low k dielectrics. Thus, it is expected that in the next future the inductor performance will benefit from this technological evolution.

On the contrary to this technological evolution, the eventual introduction of high permeability magnetic materials compatible with IC processes would have a revolutionary implication since inductor and transformer dimensions will shrink dramatically.

### 1.1.2 Modelling of Integrated Inductors

The actual performance of the integrated inductors is mainly limited by the technology characteristics. Nevertheless, their efficient use is also restricted by the partial lack of accurate models and design rules able to guide the designer towards the choice of the optimum component for a specific application. These models should provide the characteristics of the inductor (inductance, quality factor and SRF) in terms of technological parameters and the inductor layout (strip width, number of turns, distance between strips, etc).

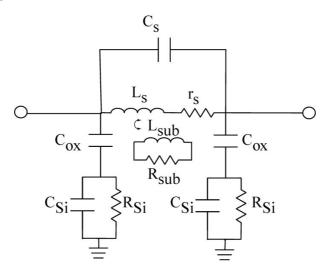

Figure 1-1. Equivalent model for an integrated inductor

An example of such an inductor equivalent model based on physical hypothesis is shown in fig.1-1. Obviously, the core of the model is an ideal inductor,  $L_s$ .  $r_s$  models the series resistance of the interconnect metallization increased by the eddy currents, and hence, it depends on the frequency. This resistance could also include the losses caused by the eddy currents induced in the Silicon substrate. However, in the model of fig. 1-1 these currents are modelled through a coupled inductor  $L_{sub}$  and an additional resistor  $R_{sub}$ . This approach gives more insight in the nature of these magnetically induced losses and in its frequency dependence [21]. Fortunately, several authors have already pointed out that for substrates with resistivities in the order of  $10\Omega cm$  these currents are negligible for frequencies below 10 GHz and hence the most common models do not include these elements [22].

Finally, the capacitor  $C_{ox}$  models the capacitance from the spiral to the substrate,  $C_{c}$  models the capacitance between the windings and  $C_{si}$  and  $R_{si}$  model the capacitance and resistance of the substrate.

These lumped models are attractive as they are easily included into standard circuit design tools. Furthermore, most of the parasitic capacitances and resistances in these models have simple, physically intuitive, analytical expressions. Unfortunately, they are not accurate enough for design purposes. To overcome this problem, EM simulators can be used to predict the behaviour of passive devices with a high degree of accuracy. However, the designer must have some expertise with these EM solvers and the design time increases due to the required computation time.

In the past many efforts have been dedicated to the elaboration of compact models based on analytical expressions (obtained from the physical behaviour) in order to save the large amount of computing time associated to EM solvers. Nowadays, thanks to the dramatic improvement of personal computers the time penalty associated to EM solvers is not as important. Still, these models can guide the designer towards the best geometry and give further insight in the optimization procedure. Thus the designer can skip the EM tools until the last steps of the design cycle are reached, when fine-tuning of the component is required.

### 1.1.3 Eddy Currents in Integrated Inductors

Once the substrate losses are minimized or removed using high resistivity substrates or micromachining techniques, the magnetically induced currents in the metal strips become important. These crowding currents or eddy currents are due to the time variation of the magnetic field and manifest themselves as a non-uniform current distribution along the strip width and not along the thickness as assumed by the skin effect.

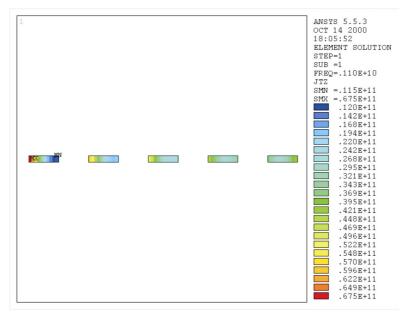

EM simulations will allow us to corroborate this point. Throughout this work, we have intensively used Momentum, an EM simulator based on the Moments method, to analyze the characteristics of integrated inductors and transformers. However, it does not offer the possibility to visualize the shape of the magnetic field generated by the

inductor or the current distribution along the strips width. Thus, we have obtained this particular data using the ANSYS quasi-static magnetic solver.

Figure 1-2. Magnetic field (in Tesla) perpendicular to the inductor plane with N=5, w=20 $\mu$ m, d=20 $\mu$ m and ri=75 $\mu$ m

Figure 1-3. Current density  $(A/m^2)$  for an inductor strips with N=5, w=20 $\mu$ m, d=20 $\mu$ m and ri=75 $\mu$ m

Previous figures show the magnetic field in the direction perpendicular to the inductor plane and the resulting current distribution across the strips width for a circular inductor with the following characteristics: 5 turns, 20  $\mu$ m of strip width, 20  $\mu$ m of distance

between strips and an inner radius of 75  $\mu m$ . In this simulation the inductor was fed with a current of 1A at 1 GHz.

The magnetic field is stronger at the centre of the inductor and decreases as we move away from it. The larger current gradients are also found for the inner turns as long as the outer turns present a much more uniform current distribution. This fact justifies the widely used hollow inductors [23], consisting in removing the inner turns of the inductor, since they do not contribute significantly to the inductance value but they suffer considerable losses magnetically induced.

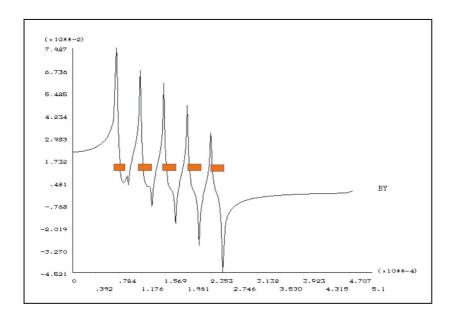

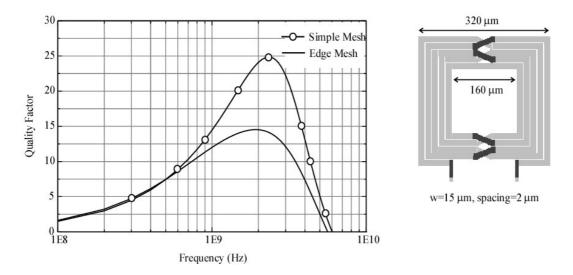

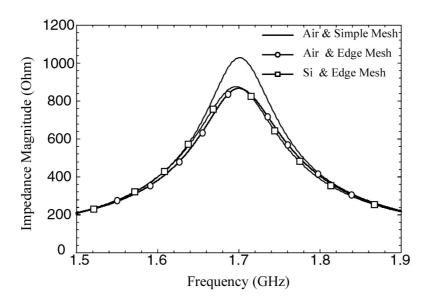

Although these crowding currents do not modify noticeably the value of the inductance [24], they cause an important increase of the effective resistance of the metal traces with the frequency and hence limit the inductor quality factor. To illustrate this fact, an inductor has been simulated under different conditions as it is done in [8]. In the first simulation, the inductor has been meshed in simple cells (just one cell along the strip width). Therefore, the effects of eddy currents are not taken into account. Then, the inductor is meshed using a more refined mesh and the strip width is split into more than one cell (3 in our particular case). The results of the simulations are shown in fig. 1-4.

Figure 1-4. Comparison of the quality factor of an integrated inductor obtained using a simple mesh (considers only ohmic losses) and an edge mesh (considers also eddy currents)

Compact inductor models take into account the losses generated by the eddy currents adding an additional term  $R_{rf}$  to the series resistor  $R_s$ , that increases with the square of the frequency, with the magnetic field strength and with the strip width [25,26,27]. For

frequencies of few GHz, the term  $R_{rf}$  may be comparable to DC resistance of the inductor. Thus, since the losses caused by these crowding currents grow with the strip width, they may prevent the improvement of the quality factor by increasing the strip width (i.e decreasing the ohmic resistance).

# 1.2 Integrated Transformers

The operation of passive transformer is based on the mutual coupling between two or more conductors, or more currently, inductors. An example of an integrated implementation it is shown in fig. 1-5 where two inductors are interwound in order to favour their mutual coupling. According to the Lenz law, the variations of the magnetic flux produced by the current flowing in the primary induce a current in the secondary winding that flows out of the terminal S. This produces a positive voltage across a load connected between terminals S and S'. Since just the variations of magnetic field generated by the primary can induce currents in the secondary, it should be noted that dc signals are blocked by the transformer allowing the windings to be biased at different voltages.

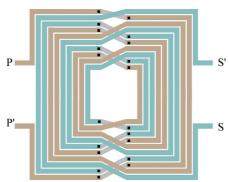

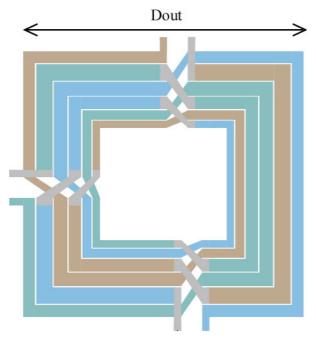

Figure 1-5. Symmetric transformer layout

The phase of the voltage induced at the secondary of the transformer depends on the choice of the reference terminal. For an ac signal source with the output and ground applied between terminals P and P', there is a minimal phase shift of the signal at the secondary if the load is connected to the terminal S (with S' grounded). This is the non-inverting connection. In the inverting connection, terminal S is grounded and S' is connected to the load so that the secondary output is antiphase to the signal applied to the primary. Aside from the phase shift between the input and the output ports, other

aspect of the transformer electrical behaviour depend on the choice of the terminal configuration [28,29].

An ideal transformer may be defined as one that is transparent to the source and the load and delivers 100% power from the source to the load without dc connection. In order to get such a performance, transformers are expected to have infinite inductance for each coil, no resistive losses in the coil conductors, 100% magnetic coupling between the primary and the secondary coils and no power losses through adjacent materials. Unfortunately, its monolithic implementation do not satisfy by far a single one of these requirements. We will analyze later in this chapter how this departure from the ideal behaviour affects the performance of circuits containing them.

In spite of their apparent limitations, integrated transformers have been used in many RFIC's such as LNA's [30], oscillators [31,32,33] and mixers [34,35] to perform functions such as impedance matching/transforming, signal coupling, phase splitting, low noise feed-back networks, etc. But probably, the most common use of a transformer in IC applications is the balun where the transformer couples a balanced (or differential) circuit to an unbalanced (single-ended) one. This can be easily accomplished by grounding the center-tap or mid-point of one transformer winding.

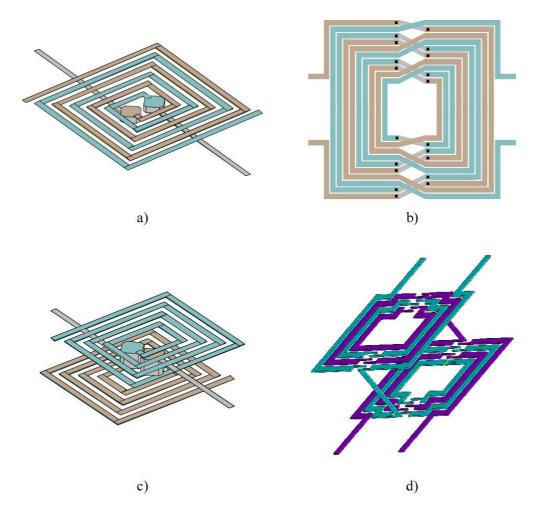

## 1.2.1 Transformer topologies

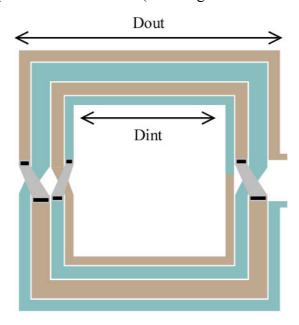

Many different structures have been proposed for integrated transformers but the most successful are shown in fig. 1-6. The first one, the SCS sided-coupled structure, exploits the magnetic coupling between two inter-wounded inductors and requires a process with two metal layers. In this topology the primary and the secondary are equal and hence it is suitable for applications demanding a symmetrical component. However, a center tap can not be established in any of the windings due to the asymmetry of the primary and the secondary. This issue can be solved using a fully symmetrical SCS topology as shown in fig. 1-6b at expense of an important increment of the number of vias. One problem with the SCS is the area efficiency. As the primary and the secondary coils are placed on every other lanes, this topology takes more silicon area compared to others structures, for the same amount of coil inductance.

Figure 1-6. Different implementations of Integrated Transformers

As an alternative to the SCS, the vertical coupling structure VCS places the primary on top of the secondary coil resulting in a higher mutual coupling due to the proximity between both spirals. Typically, the metal-to-metal spacing is less than 1 micron. Considering the pressure for low cost implementations of the RFIC's, the area efficiency is a fundamental advantage of the VCS. However, the VCS has also a couple of problems. The VCS requires a process with 3 metal layers and is not symmetric. Part of this asymmetry arises from the different thickness between metal layers in most VLSI interconnects schemes, which results in unequal resistances for the upper and lower winding. Also, the lower winding shields the upper winding from the conductive substrate, and hence the parasitic capacitance to the substrate differs for each winding. In addition, there is a large capacitance between both windings due to the overlaping of metal layers, which limits the frequency response. In many RF applications, this non-symmetric nature of the VCS can be a limiting factor for its usefulness.

Fig. 1-6d shows a transformer topology, which takes advantage of the strong points of the previous two structures [35]. Like VCS, the MCS has the advantage of the area efficiency. MCS is expected to show good mutual coupling, comparable to the VCS, not only, by the placement of the primary on top of the secondary but also by the cross-placement of the coils. Moreover, MCS is nearly symmetric and can be implemented with just double metal process. The primary or the secondary of the MCS can have higher series resistance due to the vias used to switch between the top and the bottom metal layers.

As for inductors, bond-wires can be used to implement transformers. Thus, in the bond-wire transformer proposed by [36] an individual loop consists of two bonding pads, a bond-wire and a micro-strip line. This transformer has low insertion losses due to the thick gold bond-wires. We should also mention that passive transformers have their active counterpart, but as in the case of inductors they suffer from several drawbacks as power consumption, noise or non-linearities.

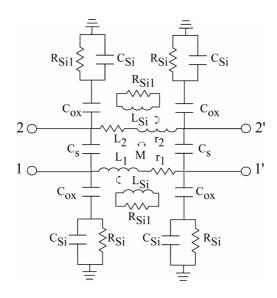

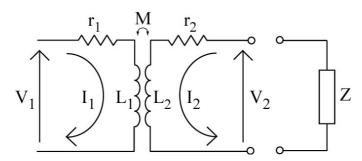

## 1.2.2 Transformer modeling

As in the inductor case, the design and optimization of circuits containing transformers requires the existence of accurate models derived from the physical layout and the process technology specifications. Unfortunately, the complete electrical behaviour of monolithic transformers can not be accurately predicted from closed-form equations, and hence numerical methods must be used. The numerical solution of Maxwell equations in three dimensions will give the most accurate results, and this technique is becoming more practical for the design of multiturn spirals transformers as computing technology and simulation software improve. Nowadays, the most common tools of circuit design already include some EM tool or some direct interface to a specific EM tool and favour its use. EM solvers also provide faster means to explore novel structures and devices before analytical models are developed.

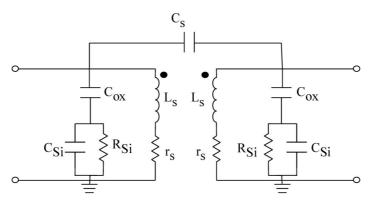

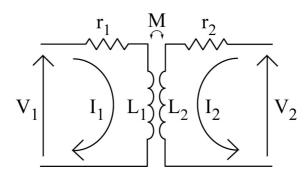

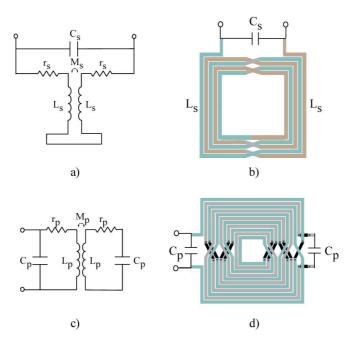

Figure 1-7. Equivalent model for an Integrated Transformer

An example of compact model for a transformer with four ports is shown in fig. 1-7. In many practical implementations, the compact model can be simplified since one or more ports are grounded and hence some devices are short-circuited. At the core of the model, there are two coupled inductors. Resistors  $r_s$  represent the ohmic losses in the windings. The interwinding capacitances are modelled by capacitors connected between the primary and the secondary  $C_s$ . The dominant capacitive parasitics between each winding and the underlying substrate are represented by the series connection of capacitors  $C_{Si}$  and  $C_{ox}$ , and substrate loss is included through the addition of a resistor  $R_{Si}$  in parallel with  $C_{Si}$ .

The definition of a loss-related figure of merit for RF transformers, in analogy to the quality factor of inductors, is not straightforward. Maybe the insertion losses could be the most important characteristic to evaluate the performance of integrated transformers since they give an idea of how efficiently a signal in the primary coil is transmitted to the secondary coil. Insertion losses are determined by metal ohmic losses, substrate dissipation, and magnetic coupling factor and can be reduced placing a tunning capacitor in shunt with each winding, at expense of narrowing the frequency bandwidth. Also, many of the techniques that have been applied to optimization of monolithic inductors are also applicable to the transformers. For example, ohmic losses are reduced when multiple layers are used to construct each winding. The current trend in Silicon technologies toward thicker and lower permitivity dielectrics will result also in improved performance from stacked winding transformers in the future.

### 1.2.3 Eddy Currents in Integrated Transformers

In the previous section, devoted to the revision of the state of the art of integrated inductors, we have given a special insight to the analysis of eddy currents. The goal of this section is to extend this analysis to the integrated transformers and to highlight some important differences existing between both components. In particular, we will try to identify any eventual cancellation of eddy currents due to the transformer effect and how it may affect the design, modelling and optimization of the component.

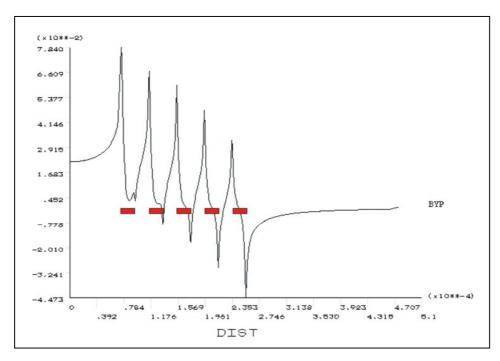

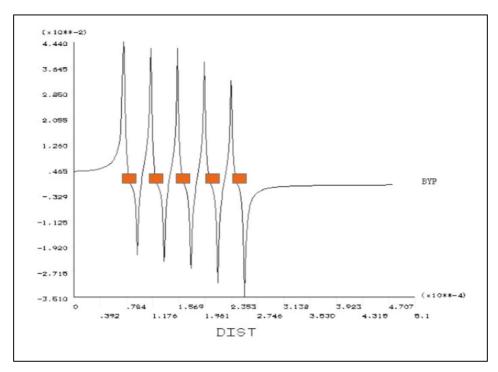

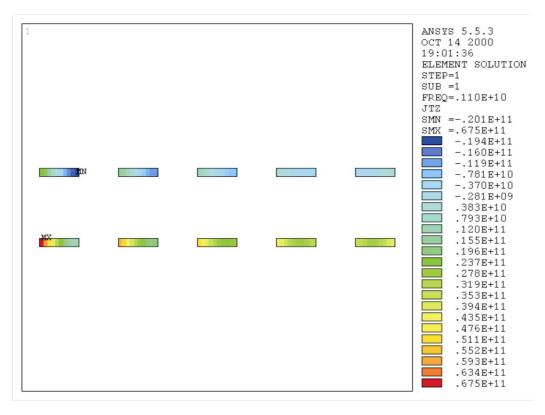

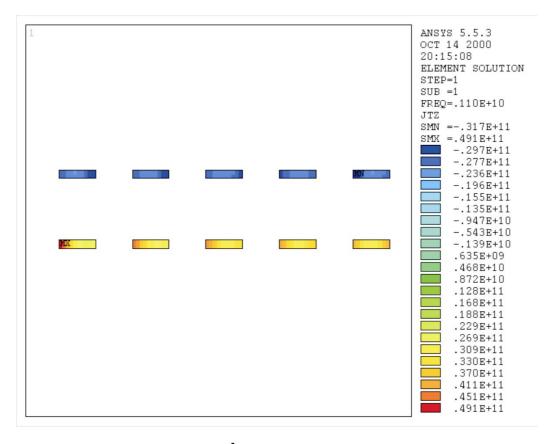

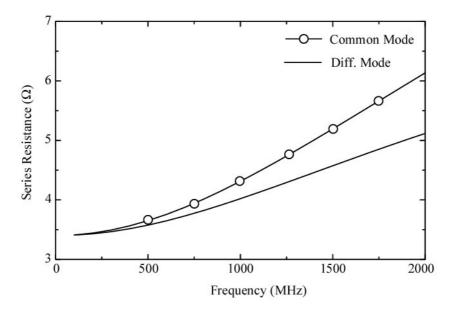

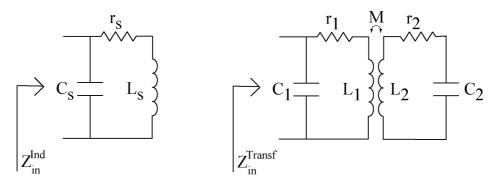

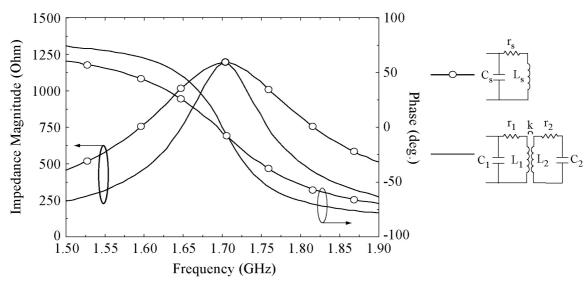

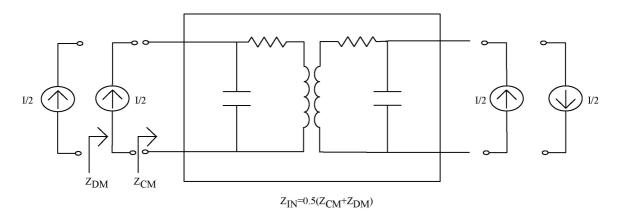

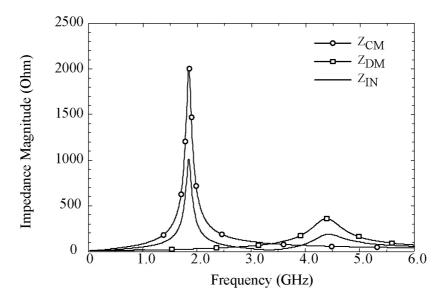

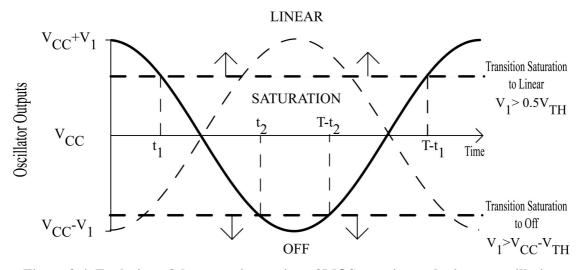

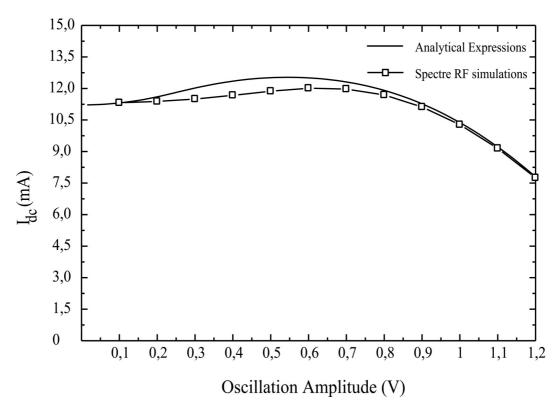

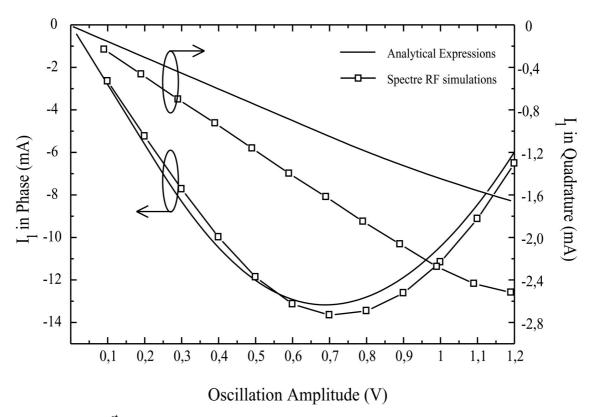

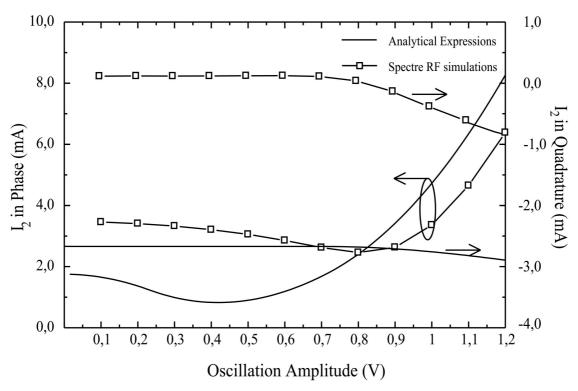

Figure 1-8. Simplified transformer model